リンクス

GINGA digital CL2e/ 4e

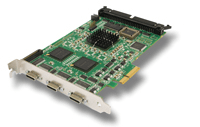

高速かつ高解像度化が進むディジタルカメラ技術に対応するために、最高のコストパフォーマンスを実現したディジタルカメラリンク対応の画像入力ボード。

PCI Expressバスを採用することで最大2.0GB/secの帯域を確保し、FullおよびMedium Configurationカメラは最大2台、Base Configurationカメラは最大4台まで接続することが可能です。各種モノクロ/カラーのカメラリンク対応カメラをサポートし、より高精細な画像処理を実現しました。

技術革新が進む産業用ディジタルカメラ業界においても、先進性の高い画像入力ボードに仕上げています。

コンテンツ

GINGA digital-CLeシリーズ 比較表

| 型番 | PCI Express スロット | PoCL | 接続可能カメラ台数 | 汎用IO | |||

|---|---|---|---|---|---|---|---|

| Base | Medium | Full | 10TAP | ||||

| GINGA-DG/CL2e-DL | x4 (1.0GB/sec) | ○※1 | 2台 | – | – | – | In4/Out10 |

| GINGA-DG/CL4e-DL | x4 (1.0GB/sec) | ○※1 | 4台 | – | – | – | In4/Out12 |

| GINGA-DG/CL2e-D (製造終了品) | x8 (2.0GB/sec) | – | 2台 | – | – | – | In5/Out8 |

| GINGA-DG/CL2e-F (製造終了品) | x8 (2.0GB/sec) | – | 1台 | 1台 | 1台 | – | In5/Out7 |

| GINGA-DG/CL2e-F-EX4 (製造終了品) | x8 (2.0GB/sec) | – | 1台 | 1台 | 1台 | 1台 | In5/Out7 |

| GINGA-DG/CL4e-D (製造終了品) | x8 (2.0GB/sec) | – | 4台 | – | – | – | In5/Out8 |

| GINGA-DG/CL4e-F (製造終了品) | x8 (2.0GB/sec) | – | 2台 | 2台 | 2台 | – | In5/Out8 |

| GINGA-DG/CL4e-F-EX4 (製造終了品) | x8 (2.0GB/sec) | – | 2台 | 2台 | 2台 | 2台 | In5/Out8 |

- 1PoCL規格、通常CL規格のどちらの規格にも対応可能

仕様

銀河digital-CL4e-DL

- Base Configuration 4チャンネル

- PCI Expressバス(x4)対応、1.0GB/sec

- PoCL対応(通常のCL規格にも対応)

- 小型カメラリンク(SDR)コネクタ×3 (4チャンネル目はオプション)

銀河digital-CL2e-DL

- Base Configuration 2チャンネル

- PCI Expressバス(x4)対応、1.0GB/sec

- ユーザによるマップ作成、ルート設定が容易

- PoCL対応(通常のCL規格にも対応)

- カメラリンク(MDR)コネクタ×2

銀河digital-CL2e-F(-EX4) / CL4e-F(-EX4)

- Base Configuration 1/2チャンネル

- Medium Configuration 1/2チャンネル

- Full Configuration 1/2チャンネル

- 10タップ Full Configuration 1/2チャンネル(-EX4モデルのみ)

- PCI Expressバス(x8)対応、2.0GB/sec

- カメラリンク(MDR)コネクタ×2

銀河digital-CL2e-D / CL4e-D

- Base Configuration 2/4チャンネル

- PCI Expressバス(x8)対応、2.0GB/sec

- カメラリンク(MDR)コネクタ×2

共通仕様

- カメラリンク対応ディジタル画像入力ボード

- 85MHzまでのクロックに対応、最大160bit

- 256K(W)×128K(H)までのカメラに対応

- 複数枚のボードを用いて同時入力

- ハードウエア/ソフトウエアトリガー、ストロボ制御可能

- エンコーダー入力対応

- フレームレートの制限なし

- オンボードメモリ不要なデータ転送アーキテクチャ

- エンコーダー入力ポート、露光制御を行うための汎用出力ポート装備

- 画像転送とパソコンCPUでの画像処理の同時処理(非同期並列処理)

- フレーム/ライン間を切れ目なく連続入力可能

- ハードウエアによるベイヤー変換(オプション)

- ハーフサイズ

- RoHS準拠

- Windows XP/Vista/7 32bit/64bit対応

- HALCON 7.1以降対応

- 仕様の異なる複数台カメラからの取り込みをお考えの場合は support@linx.jp までお問い合わせください。

カメラリンクコネクター(P1,P2)

カメラコネクターピンアサイン

基板側コネクター:

10226-1A10VE (3M)

| コネクタ | ピン番号 | 信号名 |

|---|---|---|

| CN1 | 1 | inner shield |

| PCI Express エッジから遠い | ||

| 2 | XCC4- | |

| 3 | XCC3+ | |

| 4 | XCC2- | |

| 5 | XCC1+ | |

| 6 | XSerTFG+ | |

| 7 | XSerTC- | |

| 8 | X3+ | |

| 9 | Xclk+ | |

| 10 | X2+ | |

| 11 | X1+ | |

| 12 | X0+ | |

| 13 | inner shield | |

| 14 | inner shield | |

| 15 | XCC4+ | |

| 16 | XCC3- | |

| 17 | XCC2+ | |

| 18 | XCC1- | |

| 19 | XSerTFG- | |

| 20 | XSerTC+ | |

| 21 | X3- | |

| 22 | Xclk- | |

| 23 | X2- | |

| 24 | X1- | |

| 25 | X0- | |

| 26 | inner shield |

| コネクタ | ピン番号 | 信号名 |

|---|---|---|

| CN2 | 1 | inner shield |

| PCI Express エッジに近い | ||

| 2 | YCC4- | |

| 3 | YCC3+ | |

| 4 | YCC2- | |

| 5 | YCC1+ | |

| 6 | YSerTFG+ | |

| 7 | YSerTC- | |

| 8 | Y3+ | |

| 9 | Yclk+ | |

| 10 | Y2+ | |

| 11 | Y1+ | |

| 12 | Y0+ | |

| 13 | inner shield | |

| 14 | inner shield | |

| 15 | YCC4+ | |

| 16 | YCC3- | |

| 17 | YCC2+ | |

| 18 | YCC1- | |

| 19 | YSerTFG- | |

| 20 | YSerTC+ | |

| 21 | Y3- | |

| 22 | Yclk- | |

| 23 | Y2- | |

| 24 | Y1- | |

| 25 | Y0- | |

| 26 | inner shield |

I/Oコネクター(P11)

外部との入出力信号を画像入力ボードと接続します。ベゼルから露出しない内部コネクタです。表2にピン配置を示します。CN4(I/O-0)がチャネル0、CN5(I/O-1)がチャネル1の制御に使われます。

※下表は銀河digital-CL4e-D用になります。種類により異なりますので、詳細はPDFファイルを参照ください。

I/Oコネクタピンアウト 【対応ボード】 銀河digital-CL2e-D 銀河digital-CL2e-F 銀河digital-CL4e-D 銀河digital-CL4e-F

| ピン番号 | 信号名 | 入/出 | 説明 |

|---|---|---|---|

| 1 | VFG0_TRIGGER+ | 入 | VFG0: トリガー(差動入力+) |

| 2 | VFG0_TRIGGER- | 入 | VFG0:トリガー(差動入力-) |

| 3 | VFG0_TRIGGER_TTL | 入 | VFG0:トリガー(TTL) |

| 4 | VFG0_TRIGGER_OPTO_K | 入 | VFG0:トリガー(カソード側) |

| 5 | VFG0_TRRIGER_OPTO_A | 入 | VFG0:トリガー(アノード側) |

| 6 | GND | ||

| 7 | VFG0_ENCODER+ | 入 | VFG0:エンコーダ(差動+) |

| 8 | VFG0_ENCODER- | 入 | VFG0:エンコーダ(差動-) |

| 9 | VFG0_ENCODER_TTL | 入 | VFG0:エンコーダ(TTL) |

| 10 | VFG0_ENCODER_OPTO_K | 入 | VFG0:エンコーダ(カソード側) |

| 11 | VFG0_ENCODER_OPTO_A | 入 | VFG0:エンコーダ(アノード側) |

| 12 | GND | ||

| 13 | VFG0_GPIN0_TTL | 入 | VFG0:汎用入力0(TTL) |

| 14 | VFG0_GPIN1_TTL | 入 | VFG0:汎用入力1(TTL) |

| 15 | VFG0_GPIN2+ | 入 | VFG0:汎用入力2(差動+) |

| 16 | VFG0_GPIN2- | 入 | VFG0:汎用入力2(差動-) |

| 17 | VFG0_GPIN3+ | 入 | VFG0:汎用入力3(差動+) |

| 18 | VFG0_GPIN3- | 入 | VFG0:汎用入力3(差動-) |

| 19 | VFG0_GPIN4+ | 入 | VFG0:汎用入力4(差動+) |

| 20 | VFG0_GPIN4- | 入 | VFG0:汎用入力4(差動-) |

| 21 | GND | ||

| 22 | VFG0_GPOUT0+ | 出 | VFG0:汎用出力0(差動+) |

| 23 | VFG0_GPOUT0- | 出 | VFG0:汎用出力0(差動-) |

| 24 | VFG1_GPOUT0+ | 出 | VFG1:汎用出力0(差動+) |

| 25 | VFG1_GPOUT0- | 出 | VFG1:汎用出力0(差動-) |

| 26 | VFG2_GPOUT0+ | 出 | VFG2:汎用出力0(差動+) |

| 27 | VFG2_GPOUT0- | 出 | VFG2:汎用出力0(差動-) |

| 28 | VFG0_GPOUT1_TTL | 出 | VFG0:汎用出力1(TTL) |

| 29 | GND | ||

| 30 | VFG1_GPOUT1_TTL | 出 | VFG1:汎用出力1(TTL) |

| 31 | VFG3_GPOUT0_OC | 出 | VFG3:汎用出力0(オープンコレクタ) |

| 32 | VFG3_GPOUT0_VCC | 出 | VFG3:汎用出力0(電源) |

| 33 | VFG2_GPOUT1_OC | 出 | VFG2:汎用出力1(オープンコレクタ) |

| 34 | VFG2_GPOUT1_VCC | 出 | VFG2:汎用出力1(電源) |

| 35 | GND | ||

| 36 | GND | ||

| 37 | Reserved | ||

| 38 | GND | ||

| 39 | Reserved | ||

| 40 | GND | ||

| 41 | VFG1_TRIGGER+ | 入 | VFG1: トリガー(差動入力+) |

| 42 | VFG1_TRIGGER- | 入 | VFG1:トリガー(差動入力-) |

| 43 | VFG1_TRIGGER_TTL | 入 | VFG1:トリガー(TTL) |

| 44 | VFG1_ENCODER+ | 入 | VFG1:エンコーダ(差動+) |

| 45 | VFG1_ENCODER- | 入 | VFG1:エンコーダ(差動-) |

| 46 | VFG1_ENCODER_TTL | 入 | VFG1:エンコーダ(TTL) |

| 47 | VFG2_TRIGGER+ | 入 | VFG2: トリガー(差動入力+) |

| 48 | VFG2_TRIGGER- | 入 | VFG2:トリガー(差動入力-) |

| 49 | VFG2_TRIGGER_TTL | 入 | VFG2:トリガー(TTL) |

| 50 | VFG2_ENCODER+ | 入 | VFG2:エンコーダ(差動+) |

| 51 | VFG2_ENCODER- | 入 | VFG2:エンコーダ(差動-) |

| 52 | VFG2_ENCODER_TTL | 入 | VFG2:エンコーダ(TTL) |

| 53 | VFG3_TRIGGER+ | 入 | VFG3: トリガー(差動入力+) |

| 54 | VFG3_TRIGGER- | 入 | VFG3:トリガー(差動入力-) |

| 55 | VFG3_TRIGGER_TTL | 入 | VFG3:トリガー(TTL) |

| 56 | VFG3_ENCODER+ | 入 | VFG3:エンコーダ(差動+) |

| 57 | VFG3_ENCODER- | 入 | VFG3:エンコーダ(差動-) |

| 58 | VFG3_ENCODER_TTL | 入 | VFG3:エンコーダ(TTL) |

| 59 | Reserved | ||

| 60 | VFG3_GPOUT1_TTL | 出 | VFG3:汎用出力1(TTL) |