|

実践VisualApplets: FPGA処理時間計測デザイン作成

|

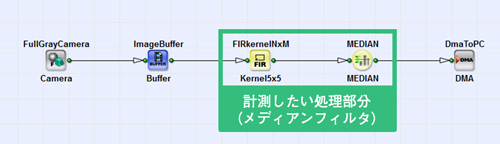

今回は、処理時間の計測として5x5のメディアンフィルタに要する時間を計測します。まずVisualAppletsでメディアンフィルタを行うプログラムデザインはこのようになり、この緑の部分が計測したい処理部分となります。

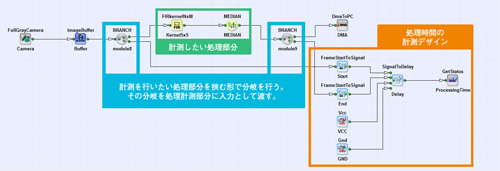

このメディアンフィルタにかかる時間を計測するプログラムは以下の様になります。計測したい処理部分を挟む形で分岐が入り、その分岐を右側オレンジの計測デザインへ渡しています。こうする事でこの水色の2つの分岐の間にどれだけの時間を要したかを計測する事が可能となります。

■

オペレーター技術解説

・[FrameStartToSignal]は、画像の先頭データが送られたタイミングで信号を生成しす。StartSignalはメディアンフィルタを行う前の先頭ピクセルのタイミングで信号を生成し、EndSignalがメディアンフィルタを終えた後の先頭ピクセルのタイミングで信号を生成します。もしメディアンフィルタが無い場合、StartSignalとEndSignalは同じとなり、処理時間はゼロとなります。

・[SignalToDelay]は2つの信号の入力に対して、どれだけのタイミング差があったかを計測します。今回はStartSignalとEndSignalのそれぞれの信号が生成されるまで何クロック要したかを計測する事で、その処理に要した時間を計測します。

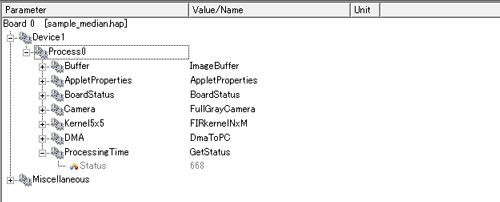

・[GetStatus]はその値をアプリケーションから数値として取得する際に使用します。これによりアプリケーションからProcessingTimeという変数名で結果の取得が可能となりました。実際に要する時間はカメラを繋いで画像を取り込みながら確認する必要があります。上記のデザインを実行すると、ProcessingTimeは以下の様になりました。

この668という値がメディアンフィルタを実行するのにFPGAが何クロックを要したかを表します。今回使用したMarathon-VCLは1回のクロックが8nsecで動作しており、そのため処理時間として5.34μ秒(668 x 8nsec)がかかっている事がわかります。

|